August 2014 Newsletter: Volume 1, Issue 3

A Message From the Director, Jian-Ping Wang

Welcome everyone to the 3rd C-SPIN Quarterly Newsletter. We have two exciting research stories: one on spin design and architecture and one on the progress we’ve made on STT-MRAM, both of which are keys to the ongoing success of our Center. For me, these stories show how our C-SPIN PIs eagerly pursue research directions beyond their traditional expertise. Thanks to Mike Lotti for his efforts to put the Newsletter together.

Industry visits. I visited Texas Instruments and Raytheon in the past few months and got a lot of new ideas about how to work more closely with our sponsors. You should know that these and other sponsors are generally impressed by the Center’s work and look forward to our progress in the quarters and years ahead.

Student/Postdoctoral fellows mini-workshop. We continue this bi-monthly effort to help our students and post-docs learn from each other. The best presenter for the July session (based on peer votes) went to Shankar Ganesh Ramasubramanian, Purdue University, and the honorable mention went to Yang Lv, University of Minnesota. Congratulations to both, and thanks to Marie Rahne for helping organize this.

Annual review September 25 and 26. This important event allows our sponsors learn about the research achievements of C-SPIN and the ongoing challenges associated with spintronic computing. All Theme leaders will give a 40-minute presentation, and several breakout sessions will be dedicated to discussing new research possibilities and ways PIs can work together more efficiently on several topics. C-SPIN-sponsored students and postdocs will also present their research at this meeting, and I expect that they will benefit from direct interaction with our sponsors. The Annual Review will be marked by a C-SPIN open house on the evening of Sept. 25, which is made possible by new office and lab space from the College of Science of Engineering at the University of Minnesota.

The View from Theme 5

- Kaushik Roy and Anand Raghunathan, Purdue University

Spin devices are unlikely to be drop-in replacements for CMOS devices, so C-SPIN PIs have to re-think circuits, architecture, and computing models. In particular, the potential of ultra-low voltage, spin-based computing will be best realized by considering new computing models that are inherently suited to the characteristics of the proposed devices. Theme 5 PIs are working closely with PIs with expertise in devices and materials to synergistically explore new kinds of spintronics devices, circuits, architectures, computing models, and applications. To the best of our knowledge, this makes Theme 5 the first ever integrated effort led by designers that aims at bringing spin technology closer to practical reality.

Based on our analysis of the potential of spin-devices, we are pursuing the following topics for this theme:

New Computing Models such as neuromorphic computing enabled by spin technology. Lateral spin valves, magnetic tunnel junctions, and domain wall magnetic strips with Spin Hall assists can operate at substantially lower voltages compared to other emerging devices (e.g. phase change devices, memristors), making them ideal for novel computing paradigms. Based on an understanding of the physics of spin transport and magnetization dynamics, we have designed and identified device structures that can naturally mimic the functionality of artificial neurons and synapses. This is of great interest to the computing world since neuro-inspired algorithms such as deep learning networks are routinely used for challenging recognition problems such as image and video analysis, web search, and data analytics. Since a network of spin devices matches the computing model very well, we see a drastic reduction in complexity compared to CMOS recognition circuitry. Moreover, these spin devices can be operated at far lower voltages than their CMOS counterparts, resulting in energy consumption improvement of one to two orders of magnitude.

Spin Transfer Torque Memories: Zero standby power and high bit cell density are the two main advantages of STT-based memory. However, STT-MRAM currently has several disadvantages with respect to write latency, write power consumption, scaling, and reliability. Theme 5 PIs are developing new device structures, bit-cells, and array designs to mitigate some of these challenges. In addition, we are also exploring how STT memory can improve computing platforms – for example, by leveraging its non-volatility for “normally-off computing” and high density to realize very large on-chip caches.

Spin Logic: Although there have been a few proposals for spin-based logic, they face significant challenges when compared to CMOS logic due to lower performance and leakage power resulting from all-metallic structure and limited spin diffusion length in interconnect materials. Theme 5 PIs have evaluated spin-based logic on complex designs such as microprocessors and identified the root causes of its inefficiency. We have shown that spin-based logic can potentially outperform CMOS in very low performance applications such as sensor nodes and bio-medical implants. New circuits and devices are under investigation to expand the applicability of spin-based logic.

Modeling: There is a need to project the characteristics of materials and devices to different levels of design abstraction (i.e. circuit, architecture and system levels). Models enable the design community to address challenges in spin-based system design and to guide future advances in spin devices. Preliminary models resulting from Theme 5 efforts in this regard have been released on the SRC website for use by the wider SRC community.

Prof. Chris Kim

Prof. Chris KimQ&A with Chris Kim on STT-MRAM

A Note from Jian-Ping Wang: In many ways, Chris Kim embodies the best of C-SPIN’s present and future. He brings his expertise on circuits, an eagerness for collaboration, and a strong sense of C-SPIN’s practical mission to his work for the Center. The result is significant progress toward viable STT-MRAM, which will be the foundation for functioning devices – and, eventually, entire computing systems – in the months and years ahead.

Q: What's the broad challenge of developing STT-MRAM?

Kim: To be really game-changing, STT-MRAM has to supersede SRAM, DRAM, and Flash technologies at the same time. This means that STT-MRAM has to be stable for long periods of time, fast, energy efficient, scalable and easily integrated with CMOS. And it should not disrupt the existing eco-system built on conventional memory technologies, which means that it should not change current interface and signal requirements.

Q: What's the best stretegy for meeting the challenge?

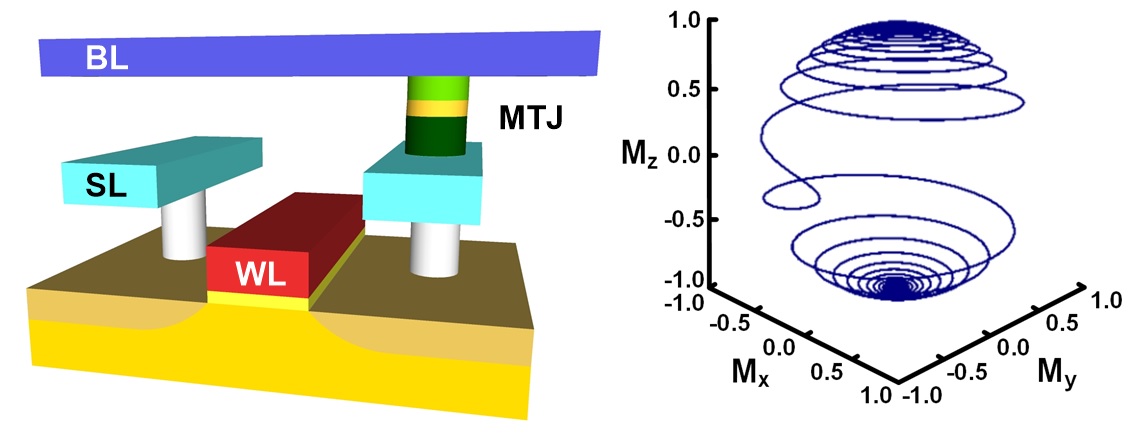

Kim: First, it’s important to realize that all of these technologies have their weaknesses, and these weaknesses will likely become more pronounced as time goes on. SRAM has leakage problems that tend to get worse as components and connections are shrunk. DRAM constantly needs to refresh, which is costly in terms of power and heat. Flash memory is non-volatile, but it has a limited lifespan because it gets damaged every time you read or write. Second, realize that the other new technologies – phase change and resistive memory – are far from proven and, in many ways, less advanced than STT-MRAM. Phase change has a promising on/off ratio, but it suffers from endurance problems. Resistive memory is still in its infancy, so it’s hard to say if it’s even promising. Third, work for C-SPIN. I know that may sound self-congratulatory, but as far as I can tell, we’re closer to making fundamental advances in STT-MRAM technology than anyone else, and we have the resources to make significant scientific discoveries in the months and years ahead. This figure shows a birds-eye view of a STT-MRAM memory cell along with the dynamic spin motion.

This figure shows a birds-eye view of a STT-MRAM memory

This figure shows a birds-eye view of a STT-MRAM memory cell along with the dynamic spin motion.

Q: Say more about the importance of C-SPIN to developing STT-MRAM.

Kim: Viable STT-MRAM is a multi-disciplinary problem. It requires new designs, new materials, and new devices, not to mention a lot of experimentation and communication. That’s why STARnet centers like C-SPIN are necessary, especially when it’s clear that CMOS will only take us so far. Having resources committed to a team of established researchers is the only way to make the progress that needs to be made.

Q: What are the biggest current challenges in developing STT-MRAM?

Kim: Bringing down the energy required to write and enhancing the read signal while maintaining good non-volatility. Like most engineering problems, developing STT-MRAM involves a fundamental trade-off between design parameters. For example, lower write energy means that the read signal is smaller and the non-volatility of the memory cell is compromised. Being able to produce a measurable difference in resistance values is another major challenge. A lot of the work lies in finding the right materials, which is why a significant amount of my C-SPIN time is spent collaborating with Theme 1 and Theme 2 PIs. Generally speaking, I tell them what an optimal resistance value is, and they figure out which materials can make that happen. Then we test, interpret results, analyze how well they scale, and move ahead – or sometimes go back to the drawing board.

Q: How much progress has been made towards viable STT-MRAM?

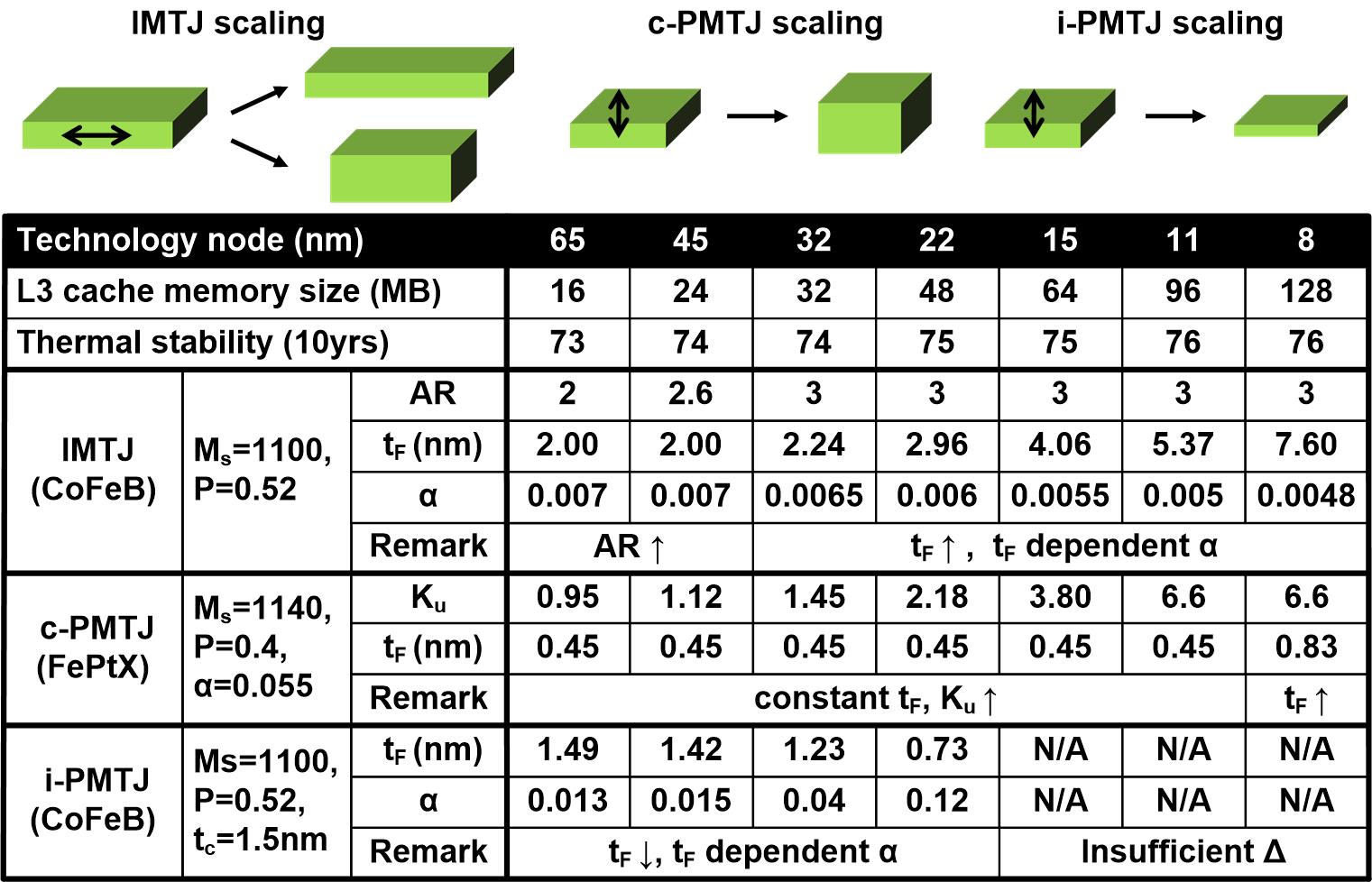

Kim: We’re much closer now than when the Center opened. We’ve more or less developed a consensus about the materials that will work, and we have developed a simulation framework for capturing the effect of scaling on STT-MRAM read and write performances. This has given us the ability to provide a detailed scaling roadmap for critical STT-MRAM metrics including switching current, switching energy, and memory cell size down to a sub-10nm technology node. It has also provided specific guidelines and directions for the materials scientists within the center. This table shows a detailed roadmap of STT-MRAM arrays based on different magnetic materials.

This table shows a detailed roadmap of STT-MRAM arrays based on different magnetic materials.

This table shows a detailed roadmap of STT-MRAM arrays based on different magnetic materials. Q: What's ahead for STT-MRAM at C-SPIN?

Kim: We have to do a lot of interface testing. Soon after that, we hope to begin fabricating and testing STT-MRAM devices. Benchmarking the different STT-MRAM candidates against existing memory technologies is important for us and our industry sponsors. Developing models and disseminating them to C-SPIN research teams, as well as other STARnet centers, is something that will make a real impact. Already, several of my students have transferred our STT-MRAM knowledge and simulation methodology to SRC companies.

Student and Post-Doc Profiles

Angeline Klemm

Angeline KlemmAngeline Klemm

Ph.D. Candidate at the University of Minnesota

I am currently working on developing lateral spin valve devices that can be used for all-spin logic applications. These devices use nano-sized ferromagnetic pillars, and our plan is to demonstrate switching of the pillars using pure spin current at room temperate. The work falls mainly under Themes 2 and 4.

My previous research was on magnetic quantum cellular automata for magnetic logic applications. I also did work on spin pumping, which developed into some of my C-SPIN work. I have seven publications to my credit and am currently in the process of submitting two papers on spin pumping in CoFeB.

I started out in a physics/engineering dual degree program at the University of Wisconsin-LaCrosse. After working as an intern in Professor Wang's lab before my junior year, I knew that I wanted to continue studying magnetics and its applications to computer memory and logic. I transferred to UMN for my senior year so that I could continue doing research in his lab. I really enjoy the hands-on learning that goes along with this work and seeing how this field can have such an impact on computing technology.

For my future career, I would really like a job that allows me to continue doing research on hard disk memory or STT-RAM (or both). It's really exciting to be working on new devices that have the potential to be used in commercial computer technologies. I hope to be a part of new breakthroughs in magnetics that can more quickly move new devices into the commercial mainstream.

Serol Turkyilmaz

Serol TurkyilmazSerol Turkyilmaz

Ph.D. Candidate at the University of California-Riverside

I am currently working on developing spin valve fabrication and spin transfer torque devices for Theme 2. The phenomena of spin polarized current transferring angular momentum to another magnetic layer can be a basic building block of a spin-based computing system. I have two pending publications related to this work.

I also do research outside the field of spintronics. I am attempting to fabricate micro-supercapacitors and devices on two-dimensional materials such as transition metal dichalcogenides, and I am studying on-chip energy storage. While working on my MS degree, I studied on-chip scale energy harvesting, and my master’s thesis was about the design and fabrication of a vibration-based MEMS energy harvester for low frequencies. My five conference presentations are related to this field.

The power of lithography still impresses me. It is amazing that billions of transistors can be placed into a relatively small area. But I’m well aware of CMOS’s limits, which is why I also find spintronics so interesting. Spintronics has the potential to overcome some of the problems in the field by being the foundation of a new way of creating and connecting circuits.

In the end, I am a learner and a doer. I can’t imagine a career without research or without applying research. That’s probably why I enjoy exploring novel device concepts and fabrication technologies – they always combine learning and doing. I plan on continuing both my learning and my doing in the semiconductor industry once I’m done with the Ph.D.